#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

32

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8SX/1650 Group

## Hardware Manual

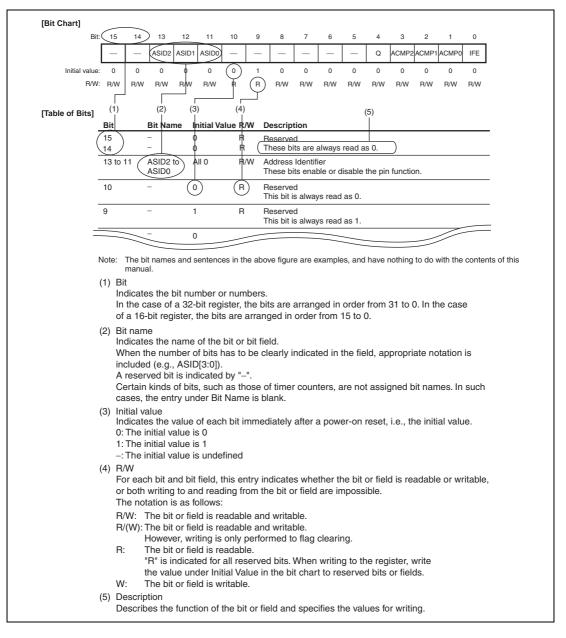

Renesas 32-Bit CISC Microcomputer H8SX Family / H8SX/1600 Series H8SX/1650C R5S61650C

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics

Rev.2.00 2007.06

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

## How to Use This Manual

#### 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for the H8SX/1650 Group. Before using any of the documents, please visit our web site to verify that you have the most up-to-date available version of the document.

| Document Type               | Contents                                                                                                                                                                   | Document Title                              | Document No.     |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|

| Data Sheet                  | Overview of hardware and electrical characteristics                                                                                                                        | _                                           | _                |

| Hardware Manual             | Hardware specifications (pin<br>assignments, memory maps,<br>peripheral specifications, electrical<br>characteristics, and timing charts)<br>and descriptions of operation | H8SX/1650 Group<br>Hardware Manual          | This manual      |

| Software Manual             | Detailed descriptions of the CPU and instruction set                                                                                                                       | H8SX Family Software<br>Manual              | REJ09B0102       |

| Application Note            | Examples of applications and<br>sample programs                                                                                                                            | The latest versions are available web site. | ailable from our |

| Renesas Technical<br>Update | Preliminary report on the specifications of a product, document, etc.                                                                                                      | -                                           |                  |

#### 2. Description of Numbers and Symbols

Aspects of the notations for register names, bit names, numbers, and symbolic names in this manual are explained below.

| (2) Register notation<br>The style "register name"_"instance number" is used in cases where there is more than one<br>instance of the same function or similar functions.<br>[Example] CMCSR_0: Indicates the CMCSR register for the compare-match timer of channel 0. (3) Number notation<br>Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary),<br>hexadecimal numbers are given as B'nnnn or 0xnnnn, and decimal numbers are given as nnnn.<br>[Examples] Binary:B'11 or 11<br>Hexadecimal: H'EFA0 or 0xEFA0<br>Decimal:1234 (4) Notation for active-low<br>An overbar on the name indicates that a signal or pin is active-low.<br>[Example] WDTOVF (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (1) | Overall notation<br>In descriptions involving the names of bits and bit fields within this manual, the modules and<br>registers to which the bits belong may be clarified by giving the names in the forms<br>"module name"."register name"."bit name" or "register name"."bit name".                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary),<br>hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn.<br>[Example3] Binary: B'11 or 11<br>Hexadecimal: H'EFA0 or 0xEFA0<br>Decimal: 1234<br>(1) Notation for active-low<br>An overbar on the name indicates that a signal or pin is active-low.<br>[Example] WDTOVF<br>(4) (2)<br>(4) (2) (2)<br>(4) (2) (2) (2) (2) (2) (2 | (2) | The style "register name"_"instance number" is used in cases where there is more than one instance of the same function or similar functions.                                                                                                                                                                                                                                 |

| An overbar on the name indicates that a signal or pin is active-low.<br>[Example] WDTOVF<br>(4 (2)<br>(4 (2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(2)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (3) | Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary),<br>hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn.<br>[Examples] Binary: B'11 or 11<br>Hexadecimal: H'EFA0 or 0xEFA0                                                                                                                      |

| 14.2.2 Compare Match Control/Status Register_0, _1 (CMCSR_0, CMCSR_1).         CMCSR indicates compare match generation, enables or disables interrupts, and selects the counter out clock. Generation of a WDTOVF grenal or interrupts the TCNT value to 0.         14.3 Opera-         14.1 CMCNT and the compare match constant register (CMCOR) match, CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the Values in CMCNT and the compare match constant register (CMCOR) match, CMCNT i (cleared to H7000) and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B101 at this time, a f/4 clock is selected.         Image: Reverse Statement in the select of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (4) | An overbar on the name indicates that a signal or pin is active-low.                                                                                                                                                                                                                                                                                                          |

| CMCSR indicates compare match generation, enables or disables interrupts, and selects the counter<br>out clock. Generation of a WDTOVF jignal or internation initializes the TCNT value to 0.<br><b>14.3 Optimize</b><br><b>14.3 Optimize</b><br><b>14.3.1 Interval Count Operation</b><br>When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in<br>CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in<br>CMSTR and the compare match constant register (CMCOR) match, CMCNT is cleared to H'0000)<br>and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this tipe,<br>a f/4 clock is selected.<br>Rev. 0.50, 10/04, page 416 of 914<br>(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | (4) (2)                                                                                                                                                                                                                                                                                                                                                                       |

| CMCSR indicates compare match generation, enables or disables interrupts, and selects the counter<br>out clock. Generation of a WDTOVF jignal or internation initializes the TCNT value to 0.<br><b>14.3 Optimize</b><br><b>14.3 Optimize</b><br><b>14.3.1 Interval Count Operation</b><br>When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in<br>CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in<br>CMSTR and the compare match constant register (CMCOR) match, CMCNT is cleared to H'0000)<br>and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this tipe,<br>a f/4 clock is selected.<br>Rev. 0.50, 10/04, page 416 of 914<br>(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | г   |                                                                                                                                                                                                                                                                                                                                                                               |

| CMCSR indicates compare match generation, enables or disables interrupts, and selects the counter<br>out clock. Generation of a WDTOVF jignal or internation initializes the TCNT value to 0.<br><b>14.3 Optimize</b><br><b>14.3 Optimize</b><br><b>14.3.1 Interval Count Operation</b><br>When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in<br>CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in<br>CMSTR and the compare match constant register (CMCOR) match, CMCNT is cleared to H'0000)<br>and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this tipe,<br>a f/4 clock is selected.<br>Rev. 0.50, 10/04, page 416 of 914<br>(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                                                                                                                                                                                                                                                                                                                                                               |

| A constraint of a WDTOVF dignal or interrunt initializes the TCNT value to 0.<br>14.3 Operation<br>14.3 Operation<br>Hand Depression of a WDTOVF dignal or interrunt initializes the TCNT value to 0.<br>14.3 Operation<br>14.3 Operation<br>14.3 Operation<br>14.3 Operation<br>CMCNT and the compare match constant register (CMCOR) match, CMCSR and the STR bit in<br>CMCNT and the compare match constant register (CMCOR) match, CMCNT is cleared to H0000)<br>and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B01 at this tipe,<br>a f/4 clock is selected.<br>Rev. 0.50, 10/04, page 416 of 914<br>(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                                                                                                                                                                                                                                                                                                                                                                               |

| <b>14.3.1 Interval Count Operation</b> When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in CMCNT and the compare match constant register (CMCOR) match, CMCNT if cleared to H10000) and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B01 at this time, a f/4 clock is selected.         RENESAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |                                                                                                                                                                                                                                                                                                                                                                               |

| <b>14.3.1 Interval Count Operation</b> When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in CMCNT and the compare match constant register (CMCOR) match, CMCNT if cleared to H10000) and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B01 at this time, a f/4 clock is selected.         RENESAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 14.3 (1)                                                                                                                                                                                                                                                                                                                                                                      |

| When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in<br>CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in<br>CMCNT and the compare match constant register (CMCOR) match, CMCNT if (cleared to H'0000)<br>and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this time,<br>a f/4 clock is selected.<br>Rev. 0.50, 10/04, page 416 of 914<br>(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | •                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in CMCNT and the compare match constant register (CMCOR) match, CMCNT if cleared to H'0000 and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this time, |

| (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | (3)                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                                                                                                                                                                                                                                                                                                                                                                               |

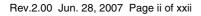

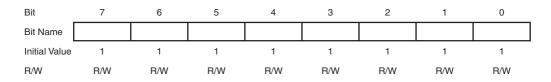

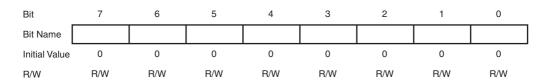

#### 3. Description of Registers

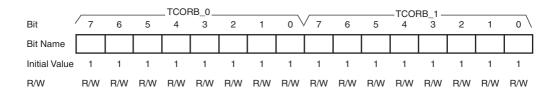

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

4. Description of Abbreviations

The abbreviations used in this manual are listed below.

• Abbreviations specific to this product

| Abbreviation | Description                    |

|--------------|--------------------------------|

| BSC          | Bus controller                 |

| CPG          | Clock pulse generator          |

| DTC          | Data transfer controller       |

| INTC         | Interrupt controller           |

| PPG          | Programmable pulse generator   |

| SCI          | Serial communication interface |

| TMR          | 8-bit timer                    |

| TPU          | 16-bit timer pulse unit        |

| WDT          | Watchdog timer                 |

#### • Abbreviations other than those listed above

| Abbreviation | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| ACIA         | Asynchronous communication interface adapter                               |

| bps          | Bits per second                                                            |

| CRC          | Cyclic redundancy check                                                    |

| DMA          | Direct memory access                                                       |

| DMAC         | Direct memory access controller                                            |

| GSM          | Global System for Mobile Communications                                    |

| Hi-Z         | High impedance                                                             |

| IEBus        | Inter Equipment Bus (IEBus is a trademark of NEC Electronics Corporation.) |

| I/O          | Input/output                                                               |

| IrDA         | Infrared Data Association                                                  |

| LSB          | Least significant bit                                                      |

| MSB          | Most significant bit                                                       |

| NC           | No connection                                                              |

| PLL          | Phase-locked loop                                                          |

| PWM          | Pulse width modulation                                                     |

| SFR          | Special function register                                                  |

| SIM          | Subscriber Identity Module                                                 |

| UART         | Universal asynchronous receiver/transmitter                                |

| VCO          | Voltage-controlled oscillator                                              |

All trademarks and registered trademarks are the property of their respective owners.

Rev.2.00 Jun. 28, 2007 Page viii of xxii

## Contents

| Secti | ion 1 C   | Overview                                     | 1  |

|-------|-----------|----------------------------------------------|----|

| 1.1   | Feature   | 2S                                           | 1  |

|       | 1.1.1     | Applications                                 | 1  |

|       | 1.1.2     | Overview of Functions                        | 2  |

| 1.2   | List of I | Products                                     | 7  |

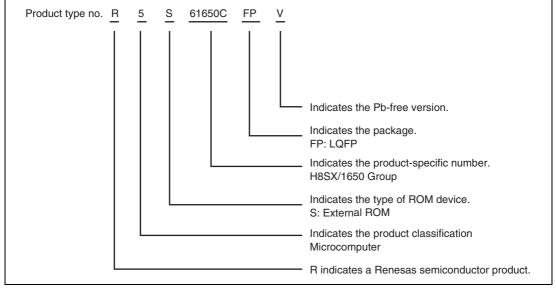

| 1.3   | Block I   | Diagram                                      |    |

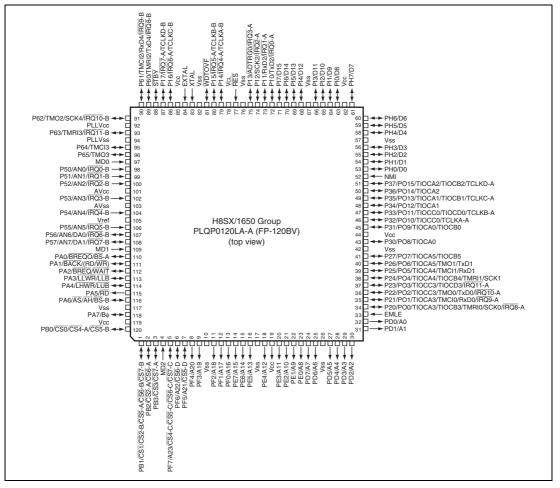

| 1.4   | Pin Ass   | signments                                    | 9  |

| 1.5   | Pin Fun   | nctions                                      |    |

| Secti | ion 2 C   | CPU                                          | 15 |

| 2.1   | Feature   | 28                                           | 15 |

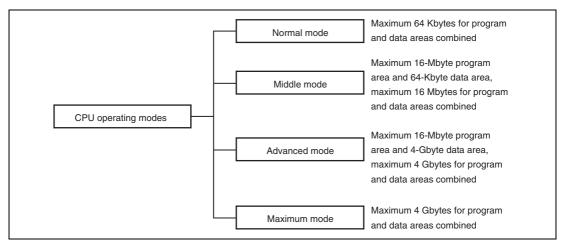

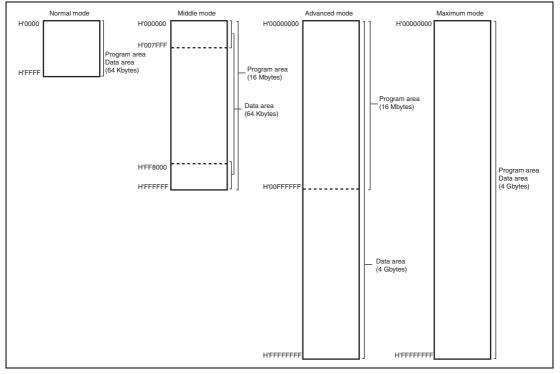

| 2.2   | CPU O     | perating Modes                               | 17 |

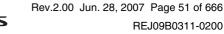

|       | 2.2.1     | Normal Mode                                  | 17 |

|       | 2.2.2     | Middle Mode                                  | 19 |

|       | 2.2.3     | Advanced Mode                                |    |

|       | 2.2.4     | Maximum Mode                                 |    |

| 2.3   | Instruct  | tion Fetch                                   |    |

| 2.4   | Address   | s Space                                      | 23 |

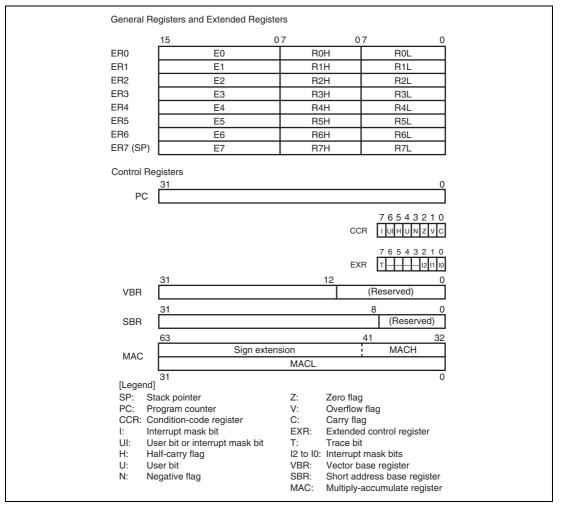

| 2.5   | Registers |                                              |    |

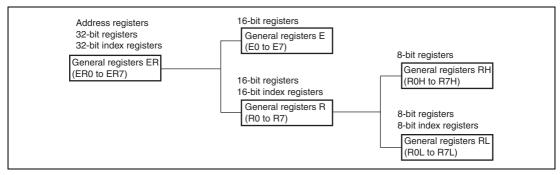

|       | 2.5.1     | General Registers                            |    |

|       | 2.5.2     | Program Counter (PC)                         |    |

|       | 2.5.3     | Condition-Code Register (CCR)                |    |

|       | 2.5.4     | Extended Control Register (EXR)              |    |

|       | 2.5.5     | Vector Base Register (VBR)                   |    |

|       | 2.5.6     | Short Address Base Register (SBR)            |    |

|       | 2.5.7     | Multiply-Accumulate Register (MAC)           |    |

|       | 2.5.8     | Initial Register Values                      |    |

| 2.6   | Data Fo   | ormats                                       |    |

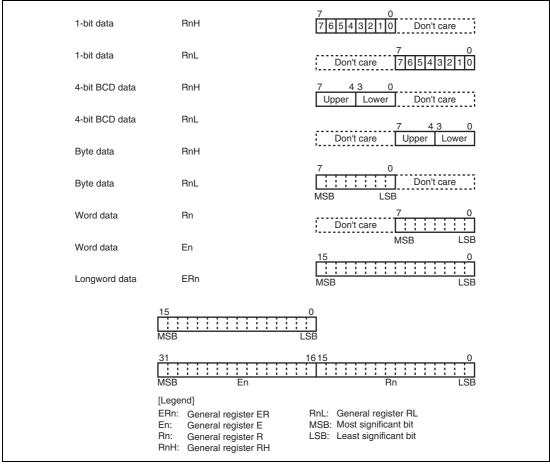

|       | 2.6.1     | General Register Data Formats                |    |

|       | 2.6.2     | Memory Data Formats                          |    |

| 2.7   | Instruct  | tion Set                                     |    |

|       | 2.7.1     | Instructions and Addressing Modes            |    |

|       | 2.7.2     | Table of Instructions Classified by Function |    |

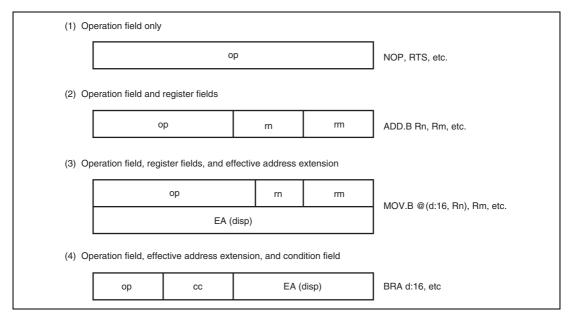

|       | 2.7.3     | Basic Instruction Formats                    |    |

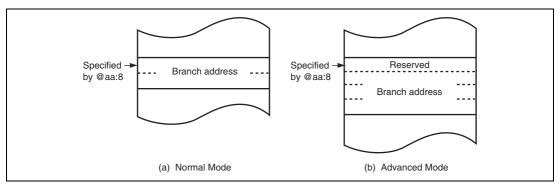

| 2.8   | Address   | sing Modes and Effective Address Calculation |    |

|       | 2.8.1     | Register Direct—Rn                           |    |

|        | 2.8.2     | Register Indirect—@ERn                                                  | . 51 |

|--------|-----------|-------------------------------------------------------------------------|------|

|        | 2.8.3     | Register Indirect with Displacement-@(d:2, ERn), @(d:16, ERn), or       |      |

|        |           | @(d:32, ERn)                                                            | . 51 |

|        | 2.8.4     | Index Register Indirect with Displacement-@(d:16,RnL.B), @(d:32,RnL.B), | ,    |

|        |           | @(d:16,Rn.W), @(d:32,Rn.W), @(d:16,ERn.L), or @(d:32,ERn.L)             | . 51 |

|        | 2.8.5     | Register Indirect with Post-Increment, Pre-Decrement, Pre-Increment,    |      |

|        |           | or Post-Decrement-@ERn+, @-ERn, @+ERn, or @ERn                          | . 52 |

|        | 2.8.6     | Absolute Address-@aa:8, @aa:16, @aa:24, or @aa:32                       |      |

|        | 2.8.7     | Immediate—#xx:8, #xx:16, or #xx:32                                      | . 54 |

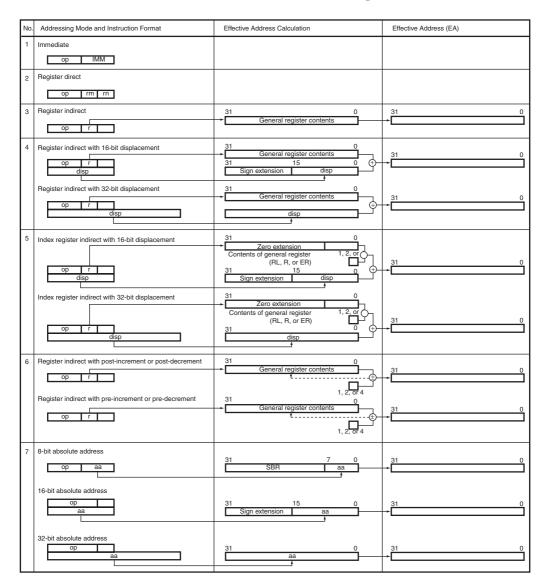

|        | 2.8.8     | Program-Counter Relative—@(d:8, PC) or @(d:16, PC)                      | . 55 |

|        | 2.8.9     | Program-Counter Relative with Index Register—                           |      |

|        |           | @(RnL.B, PC), @(Rn.W, PC), or @(ERn.L, PC)                              | . 55 |

|        | 2.8.10    | Memory Indirect—@@aa:8                                                  |      |

|        | 2.8.11    | Extended Memory Indirect—@@vec:7                                        |      |

|        | 2.8.12    | Effective Address Calculation                                           |      |

|        | 2.8.13    | MOVA Instruction                                                        |      |

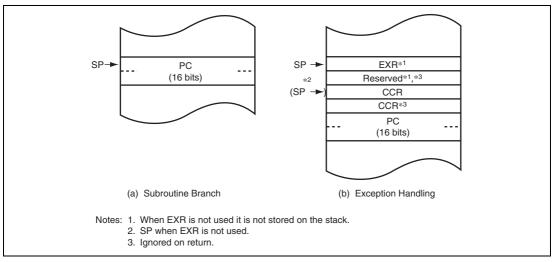

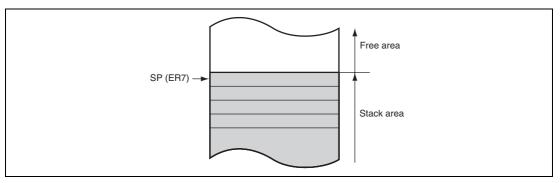

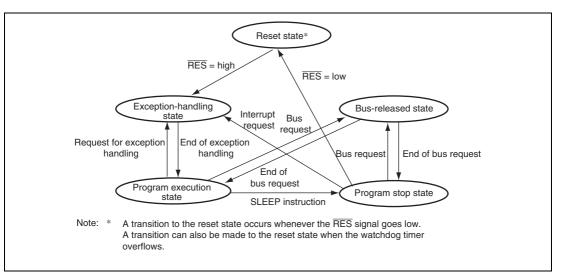

| 2.9    | Processin | g States                                                                | . 59 |

| Saati  | on 2 M    | CU Operating Modes                                                      | 61   |

| 3.1    |           | CU Operating Modes                                                      |      |

|        |           | g Mode Selection                                                        |      |

| 3.2    | 3.2.1     | Descriptions<br>Mode Control Register (MDCR)                            |      |

|        | 3.2.1     | System Control Register (MDCR)                                          |      |

| 3.3    |           | g Mode Descriptions                                                     |      |

| 5.5    | 3.3.1     | Mode 4                                                                  |      |

|        | 3.3.2     | Mode 4                                                                  |      |

|        | 3.3.3     | Pin Functions                                                           |      |

| 3.4    |           | Fill Functions                                                          |      |

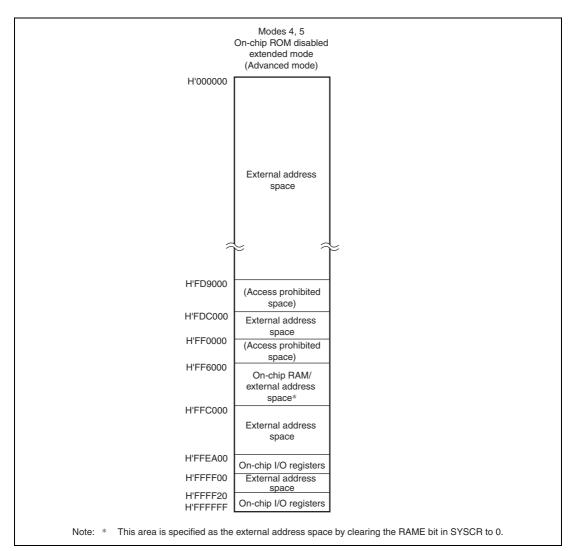

| 5.4    | 3.4.1     | Address Map (Advanced Mode)                                             |      |

|        | 5.4.1     | Address Map (Advanced Mode)                                             | . 00 |

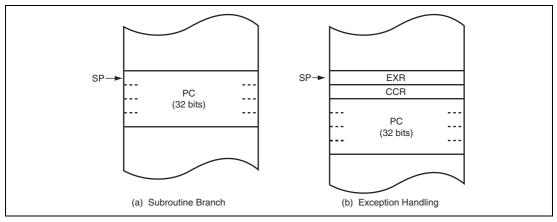

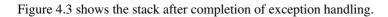

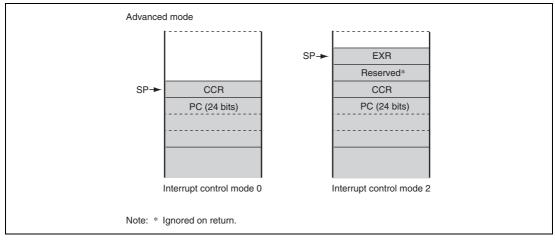

| Sectio | on 4 Ex   | ception Handling                                                        | 69   |

| 4.1    | Exception | n Handling Types and Priority                                           | . 69 |

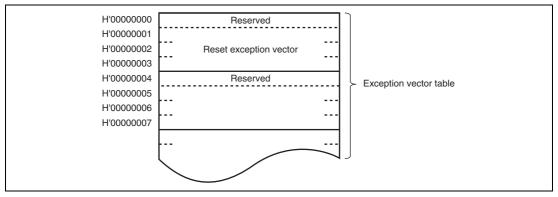

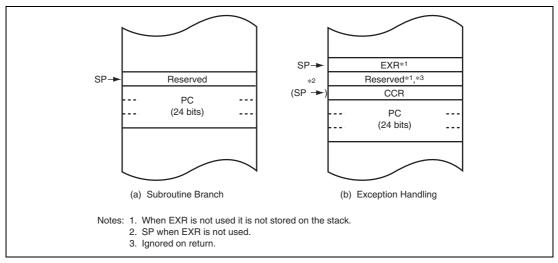

| 4.2    | Exception | n Sources and Exception Handling Vector Table                           | . 70 |

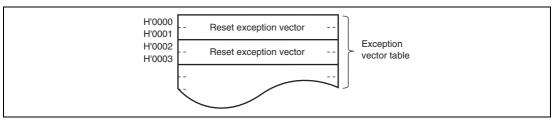

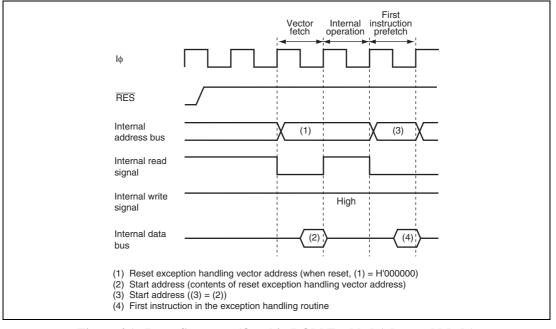

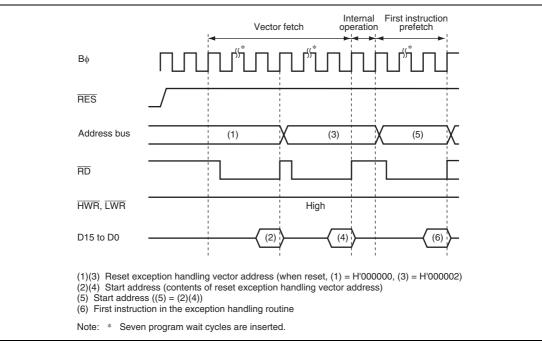

| 4.3    | Reset     |                                                                         | . 72 |

|        | 4.3.1     | Reset Exception Handling                                                | . 72 |